一、实验目的

- 掌握

16×16 LED点阵显示电路的原理。

- 学习用

VHDL语言设计较复杂电路。

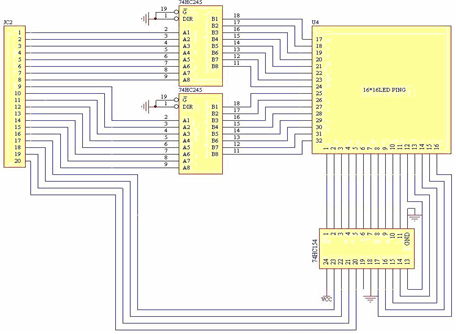

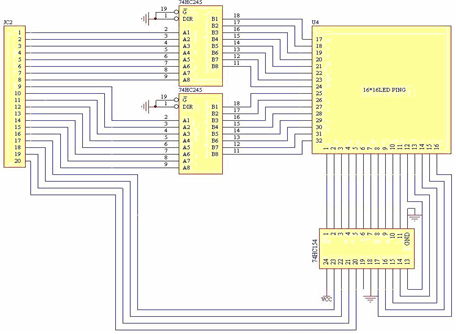

二、实验原理图

三、实验原理

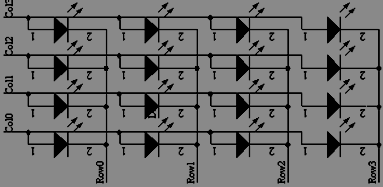

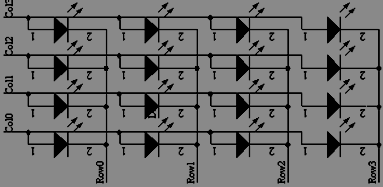

LED点阵的行为扫描选通信号,列为数据输入。显示采用逐行扫描方式,数据端不断输入数据,行扫描按一定顺序逐行选通,扫描一个周期(16次)产生一帧画面。下图以4×4共阴LED阵列为例,给出了LED阵列的组合方式,行选通低有效,数据高有效;数据端输入数据,选通行根据相应数据亮灯,接着送入第二行数据,选通第二行,依次完成一屏的扫描。只要将要显示的汉字按照16×16的点阵设计好,显示的点数据为1,不显示的点数据为0,即可将汉字显示出来。

本实验仪中16位的列数据位已与FPGA连接好,参行选通位采用地址译码方式,因此16行只需4位地址位

四、实验内容及要求

在LED点阵上循环显示2~4个汉字,内容可以是你的名字或其他汉字。(事先需用汉字点阵文件将汉字的点阵数据设计好。)

五、实验连线

- 下载前用

20芯排线连接适配板的JP3和LED点阵板的JC1插座。

- 同彩灯控制实验。

六、实验现象

在LED块中显示设计的内容。

我的vhdl代码

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

| library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity dianzhen is

port(clk1,clr,clk2: in std_logic;

addr: buffer std_logic_vector(3 downto 0);

light: out std_logic_vector(15 downto 0));

end dianzhen;

architecture behv of dianzhen is

begin

process(clk1)

begin

if clr='1' then addr<="0000";

elsif clk1'event and clk1='1' then

if addr="1111" then addr<="0000";else

addr <=addr+1;

end if;

end if;

end process;

process(addr,clk2)

variable flag: bit_vector(2 downto 0):="000";

begin

if clk2'event and clk2='1' then

if flag="000" then flag:="001";else

flag:="000";

end if;

end if;

if flag="000" then

case addr is

when "0000" => light <="0000100000000010";

when "0001" => light <="0000100001000010";

when "0010" => light <="0000100001000010";

when "0011" => light <="0000100001000010";

when "0100" => light <="0110100001000010";

when "0101" => light <="0110101001010010";

when "0110" => light <="0110101001010010";

when "0111" => light <="0100101101011010";

when "1000" => light <="0100101101011010";

when "1001" => light <="1100100101001010";

when "1010" => light <="0000100001000010";

when "1011" => light <="0001100001000010";

when "1100" => light <="0001100001000010";

when "1101" => light <="0001000001000010";

when "1110" => light <="0011000001000010";

when "1111" => light <="0110000001000010";

when others =>NULL;

end case;

else

case addr is

when "0000" => light <="0011000000000000";

when "0001" => light <="0001000111111111";

when "0010" => light <="0001000000000000";

when "0011" => light <="0000000011111110";

when "0100" => light <="1111100010000010";

when "0101" => light <="0000100010000010";

when "0110" => light <="0001000111111110";

when "0111" => light <="0011000000000000";

when "1000" => light <="0011000000000000";

when "1001" => light <="0111110111111111";

when "1010" => light <="1111010100010001";

when "1011" => light <="1011000100010001";

when "1100" => light <="0011000111111111";

when "1101" => light <="0011000100010001";

when "1110" => light <="0011000100010001";

when "1111" => light <="0011000111111111";

when others =>NULL;

end case;

end if;

end process;

end behv;

|

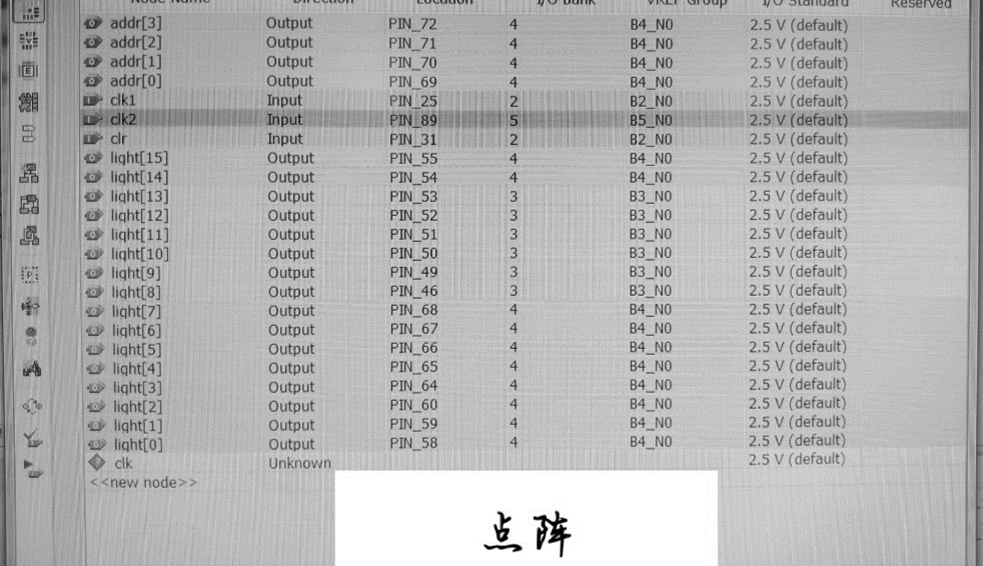

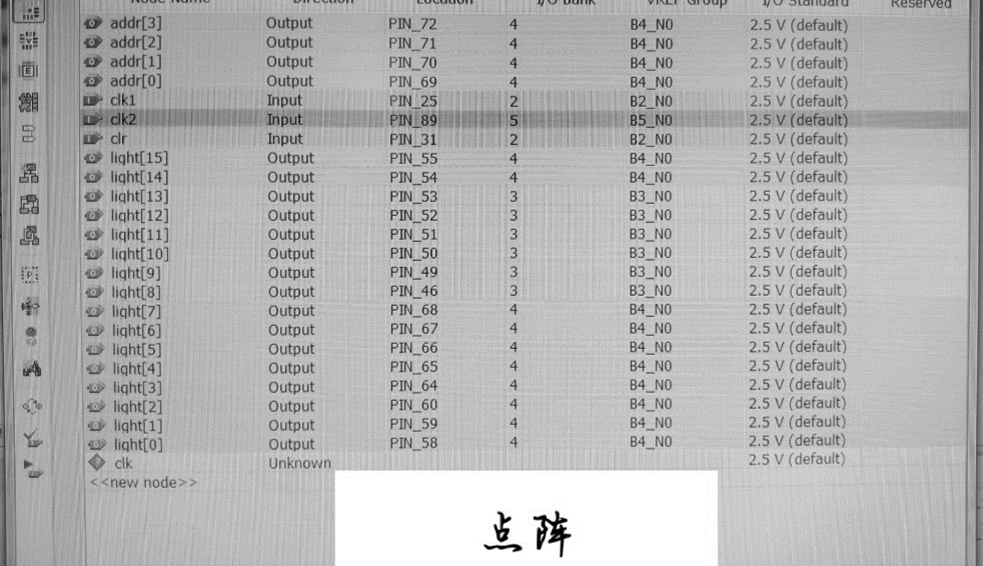

引脚连接如下: