1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

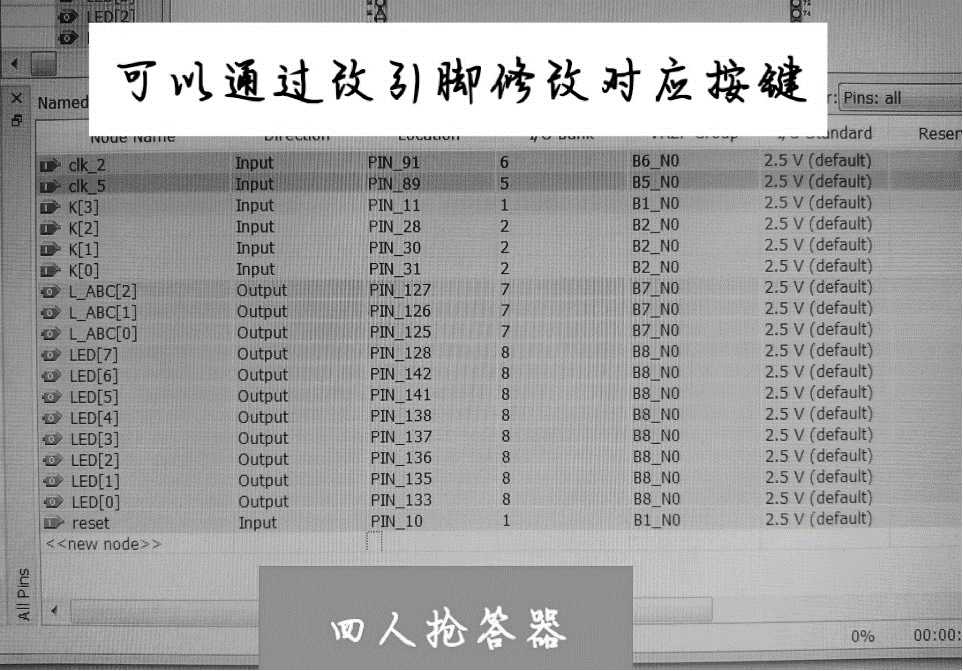

| library ieee;

use ieee.std_logic_1164.all;

entity FourManQuest is

port (K: in std_logic_vector (3 downto 0);

clk_5: in STD_LOGIC;

clk_2: in STD_LOGIC;

reset: in STD_LOGIC;

L_ABC: buffer STD_LOGIC_VECTOR(2 DOWNTO 0);

LED: out STD_LOGIC_VECTOR (7 downto 0));

end;

architecture behave of FourManQuest is

component CTL

PORT(K: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

reset: IN STD_LOGIC;

en : OUT STD_LOGIC;

D : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

end component;

component SLT_4

PORT(KD, QL, QH: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

X, Y: IN STD_LOGIC;

D: OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

end component;

component CNT_100

PORT (reset,clk,en: IN STD_LOGIC;

light: OUT STD_LOGIC;

qh,ql: BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));

end component;

component CNT_4

PORT(CLK: IN STD_LOGIC;

L_ABC: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));

end component;

component LED_8

port (A: in std_logic_vector (3 downto 0);

LED: out std_logic_vector (7 downto 0));

end component;

Signal en: STD_LOGIC;

Signal light: STD_LOGIC;

Signal D : STD_LOGIC_VECTOR(3 DOWNTO 0);

Signal DL : STD_LOGIC_VECTOR(3 DOWNTO 0);

Signal qh : STD_LOGIC_VECTOR(3 DOWNTO 0);

Signal ql : STD_LOGIC_VECTOR(3 DOWNTO 0);

begin

ctl_c: CTL port map(K, reset, en, D);

cnt_100_c: CNT_100 port map(reset, clk_5, en, light, qh, ql);

cnt_4_c: CNT_4 port map(clk_2, L_ABC);

slt_4_c: SLT_4 port map(D, ql, qh, L_ABC(1), L_ABC(0), DL);

led_8_c: LED_8 port map(DL, LED);

end behave;

|